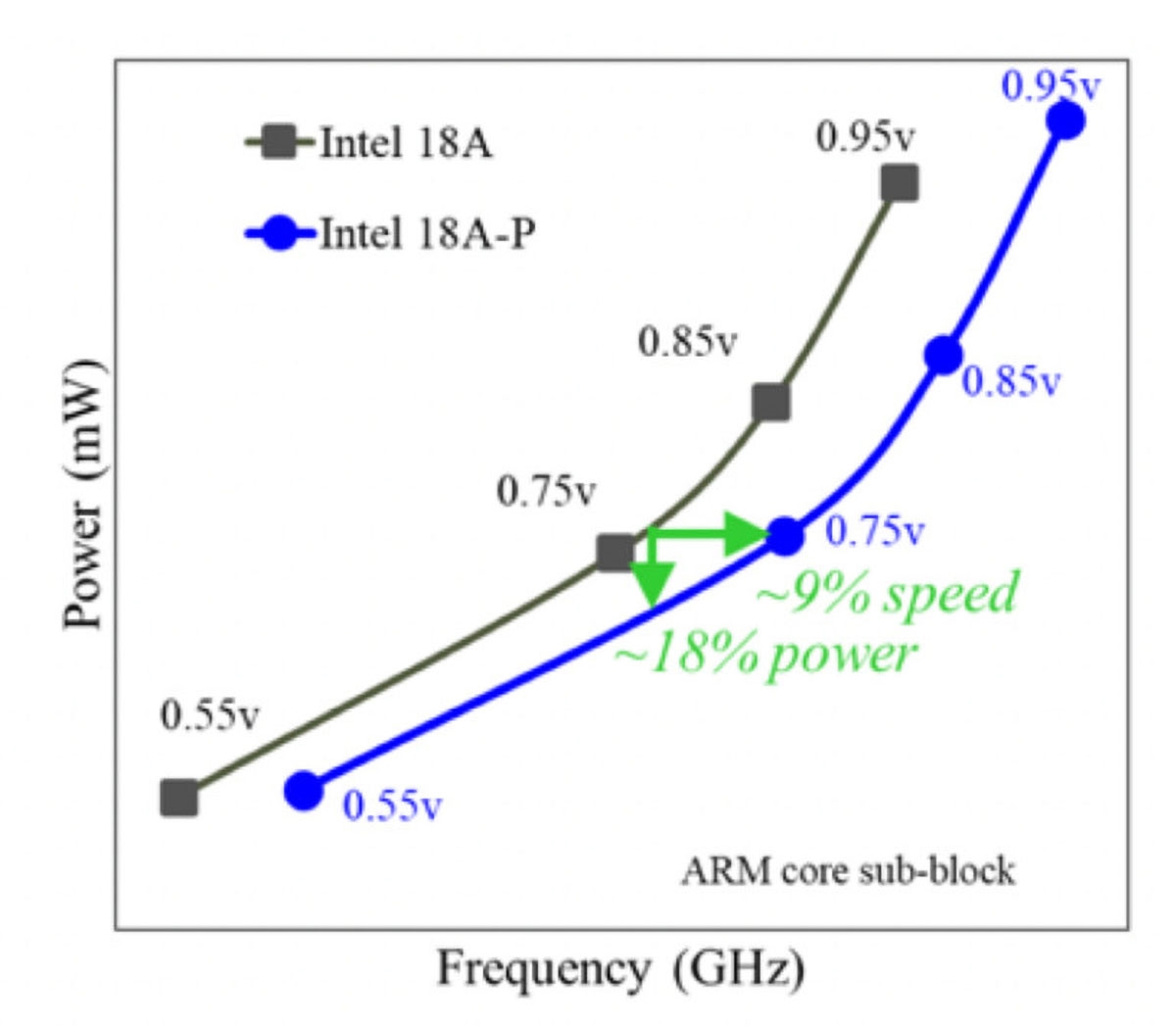

インテルは、ハワイのホノルルで開催された VLSI 2026 セミナーで、文書 T1.2 を通じてインテル 18A-P プロセス ノードの主要な技術データを正式に発表しました。標準の Intel 18A ノードと比較して、18A-P は同じ消費電力で 9% 以上のパフォーマンス向上を実現し、同じパフォーマンスで消費電力を 18% 以上削減します。

通常、世代間のノード移行でのみ見られるこの種のパフォーマンスと電力の向上は、18A-P で同じ密度で実現できるようになりました。

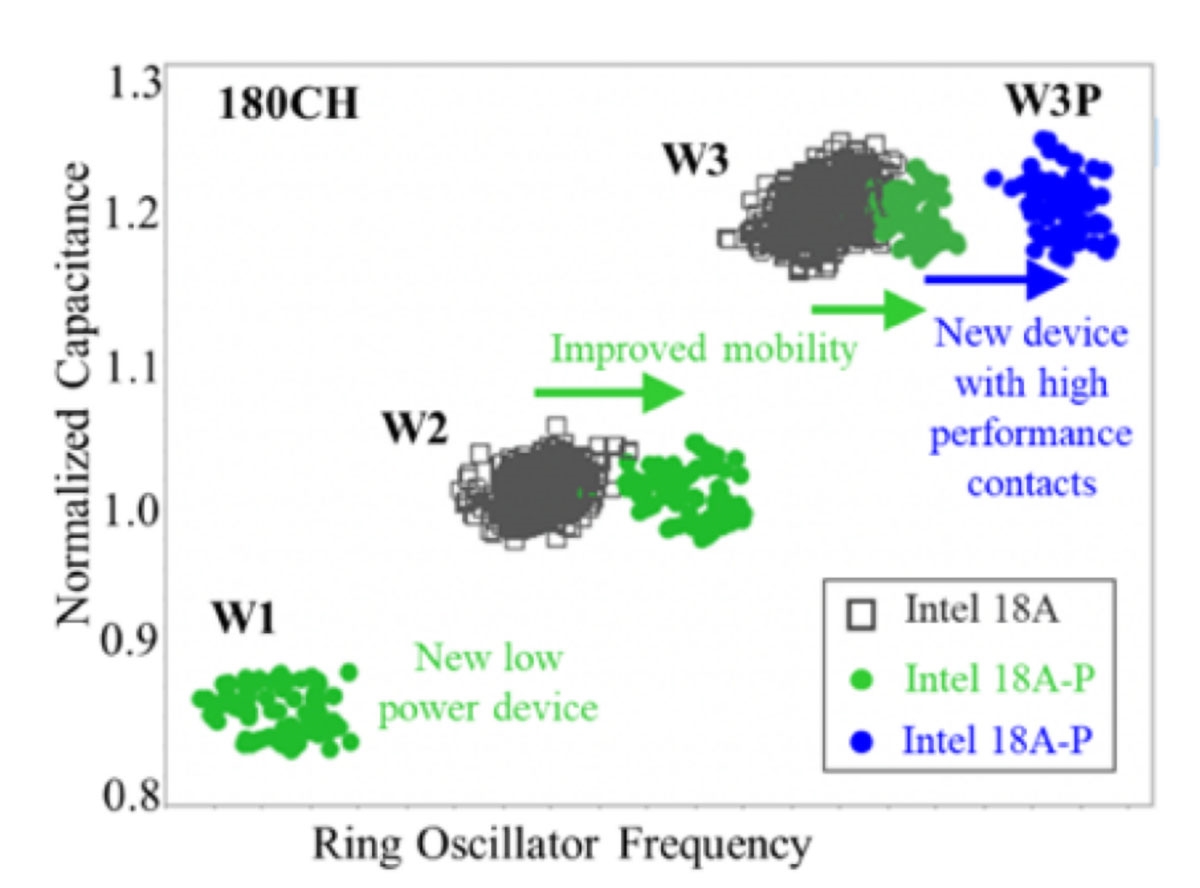

Intel のオリジナルの論文では、ロジック VT ペアの追加、より厳密なクロック オフセット角制御、高密度 (HD) および高性能 (HP) ライブラリの新しい低電力デバイス、および両方のライブラリの HP デバイスのパフォーマンス強化バージョンの 4 つの具体的な改善点が列挙されています。

Intel は、18A-P のスキュー コーナーを標準の 18A と比較して約 30% 狭めています。同一ウェーハ上のトランジスタ間の性能差が大幅に減少し、消費電力と性能特性がより予測可能になり、パラメータの歩留まりとチップの一貫性が同時に向上します。

放熱性に関しては、18A-Pは18Aに比べて熱抵抗が約50%低減され、熱伝導効率が大幅に向上しています。これは、ハイ パフォーマンス コンピューティング シナリオにおける持続的な高周波数動作にとって特に重要であり、バックサイド電源テクノロジ (PowerVia) によってもたらされる熱放散の課題にも直接対応します。

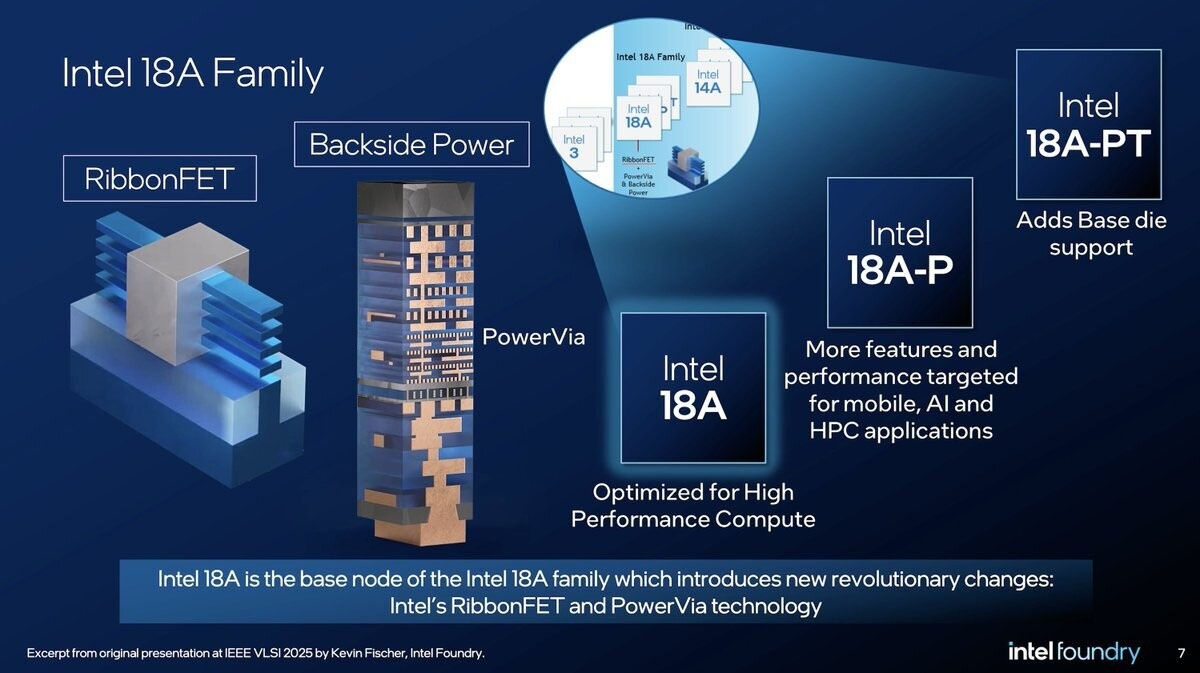

インテルは、潜在的な顧客がチップ検証のテストを開始できるように、18A-P 用の PDK プロセス設計キットのバージョン 1.0 を出荷しました。このプロセスは依然として、RibbonFET のオールラウンド ゲート トランジスタ アーキテクチャと PowerVia バック電源テクノロジに基づいており、18A プラットフォームの性能が強化されたバージョンです。

TrendForce によると、Apple は M シリーズ チップの製造に 18A-P プロセスの使用を評価しており、Google は TPU v8e プロジェクトを推進するために Intel の EMIB 高度パッケージング技術の使用を検討しているとのことです。関連製品は早ければ2027年にも発売される可能性がある。